[Mano의 컴퓨터시스템구조] 디지털 논리회로 - 플립플롭

Posted: Updated:

컴퓨터 구조 스터디를 하며 ‘Mano의 컴퓨터시스템구조 제3판’ 교재를 정리한 글입니다.

플립플롭

모든 디지털 시스템은 조합 회로를 가지고 있지만, 순차회로로 구현되는 저장요소가 필요하다.

플립플롭은 1비트 데이터를 저장하는 이진 셀(cell)이다.

입력 펄스가 상태 변환을 일으키기 전까지 이진 상태를 그대로 유지한다.

순차회로

입력 신호뿐만 아니라 현재 상태도 고려하여 출력이 결정되는 회로이다.

대부분의 순차 회로는 동기형(synchronous) 회로로, 클럭 펄스(clock pulse)를 기준으로 작동한다.

동기형 회로는 클럭의 타이밍 문제(clock skew 등)로 인해 불안정해질 가능성이 있다.

클럭 신호: 주기적인 전기 신호로 디지털 회로의 동작 시간적으로 제어

동기화: 클럭 신호를 기준으로 회로 내 모든 구성 요소가 동시에 상태를 변경하거나 동작하도록 하는 것

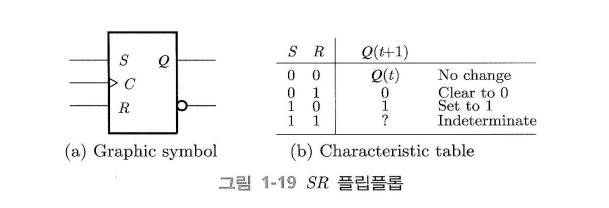

$SR$ 플립플롭

$S$(set), $R$(reset), $C$(clock) 세 개의 입력과 하나의 출력 $Q$를 가지고 있다.

$C$의 화살표 기호는 동적입력(dynamic input)으로, 플립플롭이 입력 클럭 신호의 상승 변이에서 동작한다는 의미이다.

$C$에 신호가 들어오지 않을 경우, $S$나 $R$ 입력의 값에 관계없이 출력은 변하지 않는다.

클럭 신호가 0에서 1로 변하면 $S=1$이고 $R=0$이면 출력 $Q$는 1, $S=0$이고 $R=1$이면 출력 $Q$는 0이 된다.

$S$와 $R$이 모두 0일 때 클럭 입력이 변하면 출력은 변화가 없다.

$S$와 $R$이 모두 1인 경우 출력값을 예상할 수 없으므로 회로 설계에서 피해야 한다.

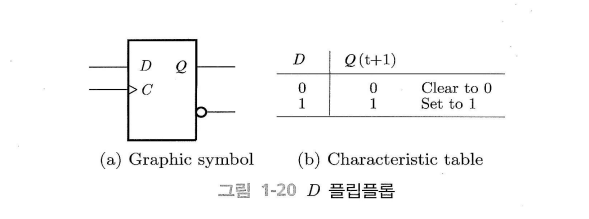

$D$ 플립플롭

$SR$ 플립플롭에서 발전된 형태로, $S$와 $R$ 입력을 인버터로 연결하고 $D$ 기호를 붙인 것이다.

$D$ 입력이 0에서 1로 클럭 변이가 발생할 때 출력 $Q$에 전달된다.

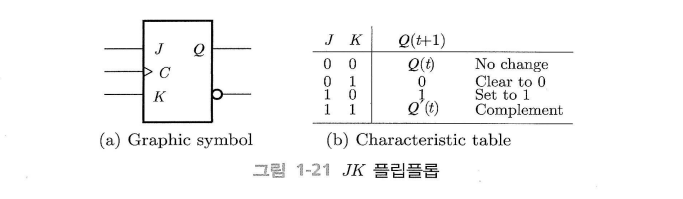

$JK$ 플립플롭

$SR$ 플립플롭의 한계를 보완한 플립플롭이다.

입력의 $K$와 $K$ 는 각각 $SR$ 플립플롭의 $S$와 $R$에 해당한다.

$J=K=1$일 때 클럭 펄스는 플립플롭의 출력을 보수로 만든다.

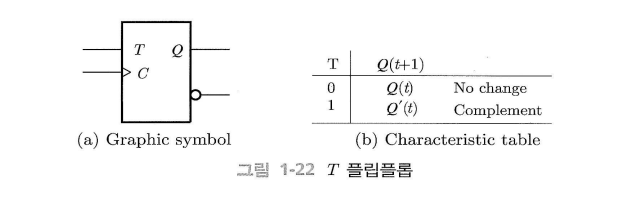

$T$ 플립플롭

토글(Toggle) 동작을 수행하는 플립플롭이다.

입력 신호로 $T$ 하나만 가진다.

$T=0$인 경우 상태 변화가 없고, $T=1$인 경우 상태는 보수로 된다.

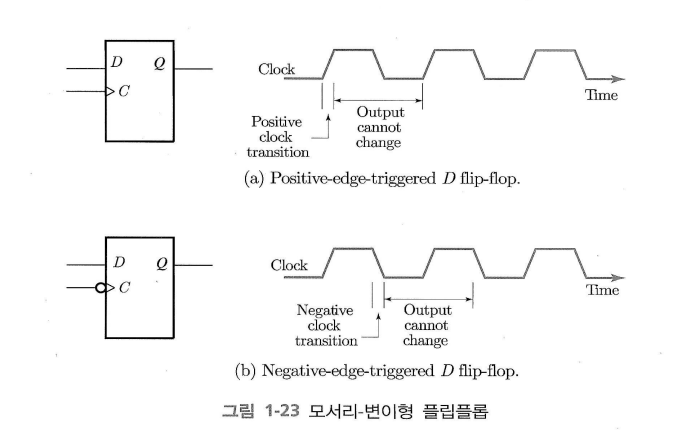

모서리-변이형 플립플롭

클럭 펄스의 변이가 발생할 때만 입력 데이터를 받아들이고 출력 상태를 변경한다.

클럭 신호가 상승하거나 하강할 때만 작동한다.

셋업 시간(setup time)과 홀드 시간(hold time)이 필요하다.

셋업 시간: 입력 값이 클럭 신호의 변이가 발생하기 전에 안정된 상태로 유지되어야 하는 최소 시간

홀드 시간: 클럭 신호 변이 이후에도 입력 값이 안정된 상태로 유지되어야 하는 최소 시간

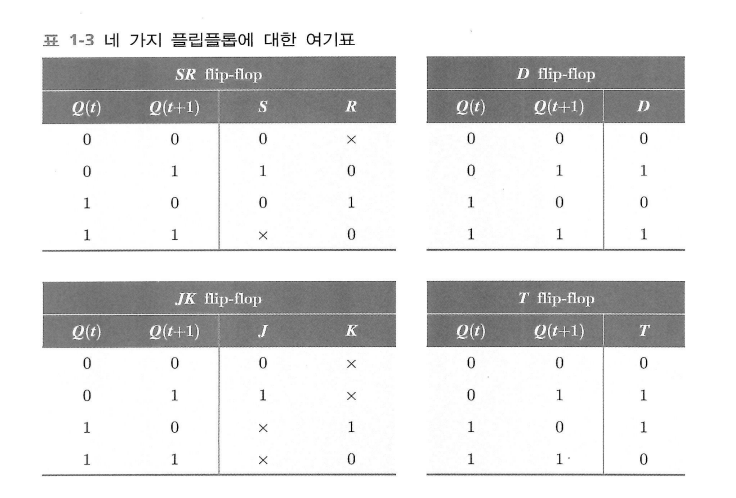

여기표

여기표는 플립플롭에서 현재 상태와 다음 상태를 알 때, 플립플롭에 어떤 입력을 넣어야 하는가를 표로 만든 것이다.

댓글남기기